- 您现在的位置:买卖IC网 > Sheet目录369 > W949D2CBJX5E (Winbond Electronics)IC LPDDR SDRAM 512MBIT 90VFBGA

�� �

�

�

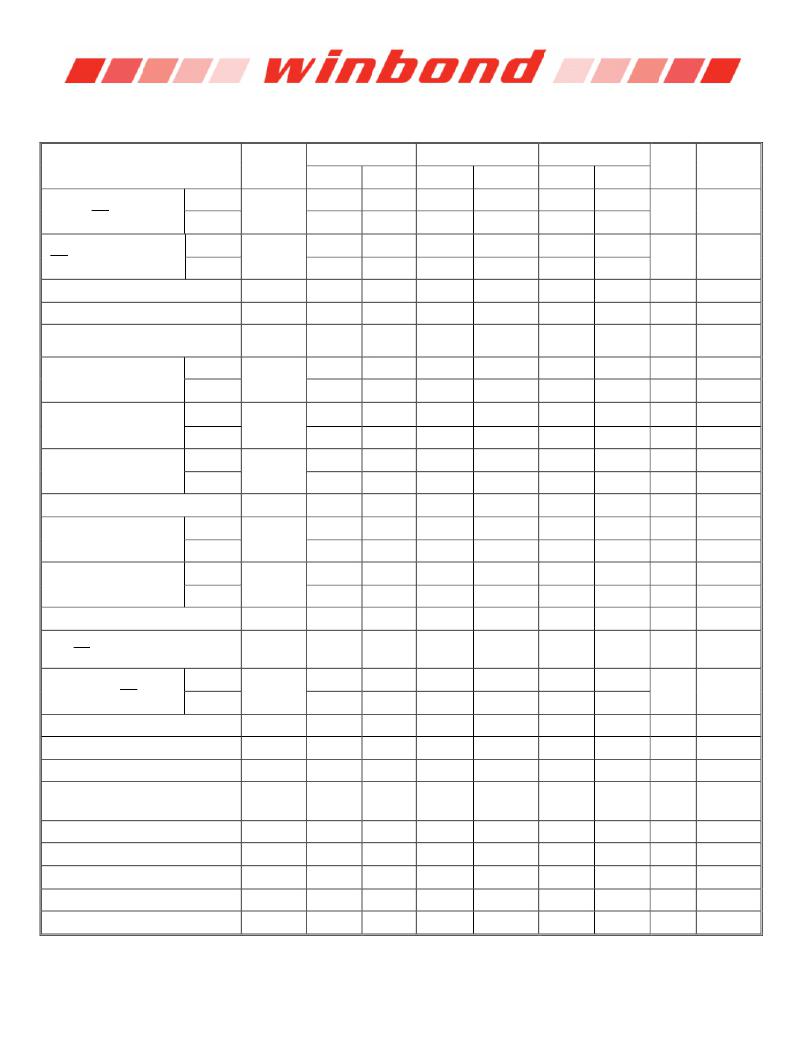

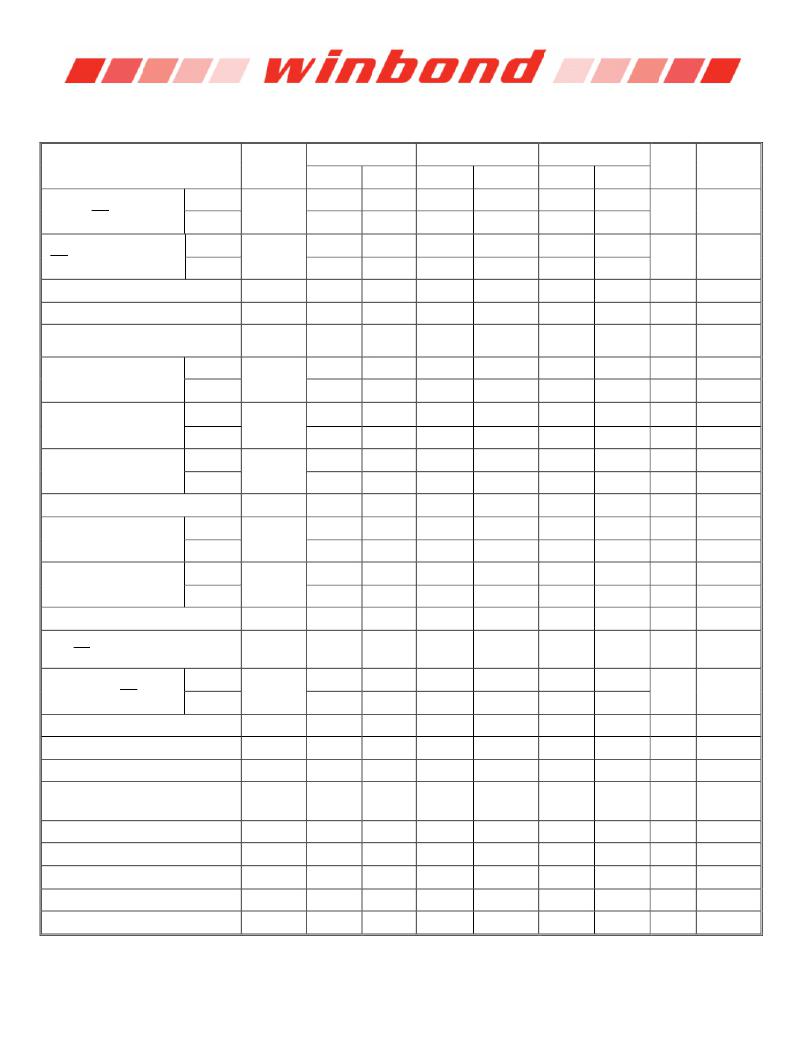

�W949D6CB� /� W949D2CB�

�512Mb� Mobile� LPDDR�

�8.5� AC� Timings�

�[Recommended� Operating� Conditions:� Notes� 1-9]�

�-5�

�-6�

�-� 75�

�PARAMETER�

�SYMBOL�

�UNIT�

�NOTES�

�MIN�

�MAX�

�MIN�

�MAX�

�MIN�

�MAX�

�DQ� output� access� time�

�from� CK/� CK�

�CL=3�

�CL=2�

�tAC�

�2.0�

�2.0�

�5.0�

�6.5�

�2.0�

�2.0�

�5.0�

�6.5�

�2.0�

�2.0�

�6.0�

�6.5�

�ns�

�DQS� output� access� time� from� CK/�

�CK�

�Clock� high-level� width�

�Clock� low-level� width�

�Clock� half� period�

�CL=3�

�CL=2�

�tDQSCK�

�tCH�

�tCL�

�tHP�

�2.0�

�2.0�

�0.45�

�0.45�

�Min�

�(tCL,� tCH)�

�5.0�

�6.5�

�0.55�

�0.55�

�2.0�

�2.0�

�0.45�

�0.45�

�Min�

�(tCL,� tCH)�

�5.0�

�6.5�

�0.55�

�0.55�

�2.0�

�2.0�

�0.45�

�0.45�

�Min�

�(tCL,� tCH)�

�6.0�

�6.5�

�0.55�

�0.55�

�ns�

�tCK�

�tCK�

�ns�

�10,11�

�CL=3�

�5�

�6�

�7.5�

�ns�

�12�

�Clock� cycle� time�

�tCK�

�CL=2�

�12�

�12�

�12�

�ns�

�12�

�DQ� and� DM� input� setup�

�time�

�fast�

�slow�

�fast�

�tDS�

�0.48�

�0.58�

�0.48�

�0.6�

�0.7�

�0.6�

�0.8�

�0.9�

�0.8�

�ns�

�ns�

�ns�

�13,14,15�

�13,14,16�

�13,14,15�

�DQ� and� DM� input� hold� time�

�tDH�

�slow�

�0.58�

�0.7�

�0.9�

�ns�

�13,14,16�

�DQ� and� DM� input� pulse� width�

�tDIPW�

�1.6�

�1.6�

�1.8�

�ns�

�17�

�Address� and� control� input�

�setup� time�

�Address� and� control� input�

�hold� time�

�fast�

�slow�

�fast�

�slow�

�tIS�

�tIH�

�0.9�

�1.1�

�0.9�

�1.1�

�1.1�

�1.3�

�1.1�

�1.3�

�1.3�

�1.5�

�1.3�

�1.5�

�ns�

�ns�

�ns�

�ns�

�15,18�

�16,18�

�15,18�

�16,18�

�Address� and� control� input� pulse� width�

�DQ� &� DQS� low-impedance� time� from�

�CK/� CK�

�tIPW�

�tLZ�

�2.3�

�1.0�

�2.6�

�1.0�

�2.6�

�1.0�

�ns�

�ns�

�17�

�19�

�DQ� &� DQS� high-impedance�

�time� from� CK/� CK�

�CL=3�

�CL=2�

�tHZ�

�5.0�

�6.5�

�5.0�

�6.5�

�6.0�

�6.5�

�ns�

�19�

�DQS-DQ� skew�

�DQ/DQS� output� hold� time� from� DQS�

�Data� hold� skew� factor�

�tDQSQ�

�tQH�

�tQHS�

�tHP-tQHS�

�0.4�

�0.5�

�tHP-tQHS�

�0.5�

�065�

�tHP-tQHS�

�0.6�

�0.75�

�ns�

�ns�

�ns�

�20�

�11�

�11�

�Write� command� to� 1st� DQS� latching�

�transition�

�DQS� input� high-level� width�

�DQS� input� low-level� width�

�tDQSS�

�tDQSH�

�tDQSL�

�0.75�

�0.4�

�0.4�

�1.25�

�0.6�

�0.6�

�0.75�

�0.4�

�0.4�

�1.25�

�0.6�

�0.6�

�0.75�

�0.4�

�0.4�

�1.25�

�0.6�

�0.6�

�tCK�

�tCK�

�tCK�

�DQS� falling� edge� to� CK� setup� time�

�DQS� falling� edge� hold� time� from� CK�

�MODE� REGISTER� SET� command�

�tDSS�

�tDSH�

�tMRD�

�0.2�

�0.2�

�2�

�0.2�

�0.2�

�2�

�0.2�

�0.2�

�2�

�tCK�

�tCK�

�tCK�

�Publication� Release� Date:� Sep,� 21,� 2011�

�-� 51� -�

�Revision� A01-007�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W971GG6JB25I

IC DDR2 SDRAM 1GBIT 84WBGA

W971GG8JB-25

IC DDR2 SDRAM 1GBIT 60WBGA

W9725G6IB-25

IC DDR2-800 SDRAM 256MB 84-WBGA

W9725G6JB25I

IC DDR2 SDRAM 256MBIT 84WBGA

W9725G6KB-25I

IC DDR2 SDRAM 256MBIT 84WBGA

W972GG6JB-3I

IC DDR2 SDRAM 2GBITS 84WBGA

W9751G6IB-25

IC DDR2-800 SDRAM 512MB 84-WBGA

W9751G6KB-25

IC DDR2 SDRAM 512MBIT 84WBGA

相关代理商/技术参数

W949D2CBJX5ETR

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 200MHZ

W949D2CBJX5I

制造商:Winbond Electronics Corp 功能描述:DRAM Chip Mobile LPDDR SDRAM 512M-Bit 16Mx32 1.8V 90-Pin VFBGA

W949D2CBJX5I TR

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 200MHZ, INDUST

W949D2CBJX6E

制造商:Winbond Electronics Corp 功能描述:DRAM Chip Mobile LPDDR SDRAM 512M-Bit 16Mx32 1.8V 90-Pin VFBGA

W949D2CBJX6ETR

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 166MHZ, 65NM

W949D2CBJX6G

制造商:WINBOND 制造商全称:Winbond 功能描述:512Mb Mobile LPDDR

W949D2KBJX5E

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 200MHZ 制造商:Winbond Electronics Corp 功能描述:IC MEMORY

W949D2KBJX5I

制造商:Winbond Electronics Corp 功能描述:IC MEMORY